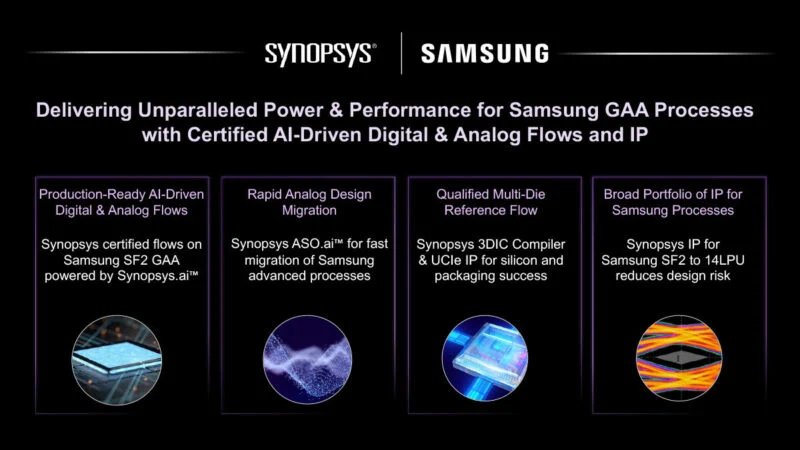

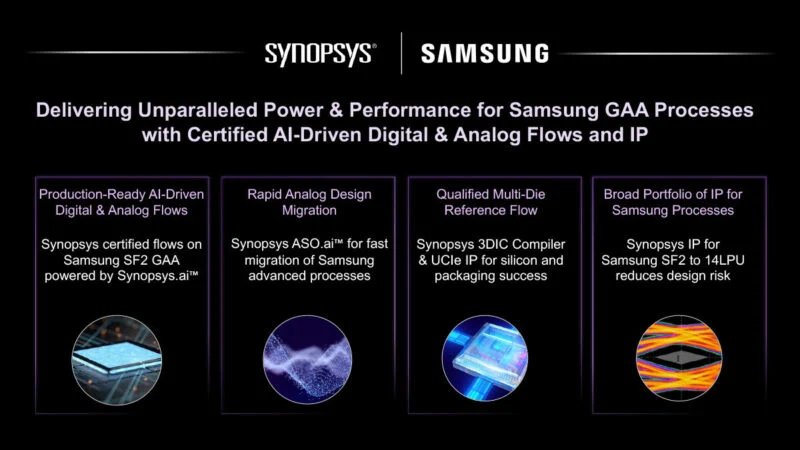

Synopsys je sporočil, da so njegova orodja za oblikovanje in IP pripravljena za 2. proizvodni postopek v livarnah Samsung Wafer.Samsung je pred kratkim sporočil, da bo leta 2025 množično proizvedel 2NM procesne čipe in izjavil, da se bo postopek še izboljšal leta 2027. Synopsys 'EDA Design Tool je prešlo Samsungovo certifikat 2NM GAA procesa.

Po uradnem uvodu lahko Synopsys 'EDA komplet izboljša migracijo simulacije, PPA (učinkovitost območja, učinkovitost in energetska učinkovitost) ter produktivnost procesnih vozlišč Samsung Wafer 2NM GAA.Synopsys uporablja umetno inteligenco (AI) za skupno optimizacijo, da bi Samsungu pomagal izboljšati učinkovitost območja, uspešnost in energetsko učinkovitost 2. procesa.

Synopsys 'DSO.AI in ASO.AI so uspešno preselili iz Finfeta v arhitekturo GAA, kar pomeni, da lahko kupci svoje obstoječe zasnove čipa Finfet gladko preselijo v nov postopek 2. GAA.

Čipična podjetja lahko uporabljajo orodja Synopsys za razvoj novih tehnologij oblikovanja čipov, vključno z ožičenjem na zadnje napajalne napajanja, metodami zaznavanja lokalnih postavitve in oblikovanje enote nanosheet, s čimer se izboljšajo učinkovitost in delovanje procesov SF2.Samsung je izjavil, da lahko procesno vozlišče SF2Z še izboljša učinkovitost, porabo energije in gostoto (za 20%).

Synopsys je razkril tudi, da je bil njegov UCIE IP uporabljen pri proizvodnji čipov na procesnih vozliščih Samsung SF2 in SF4X.Poleg tega bo enaka rešitev DTCO uporabljena tudi za optimizacijo Samsungovega 1,4 nm procesnega vozlišča (SF1.4).